集成电路专业教学一体化解决方案

自动评测实验环境

●

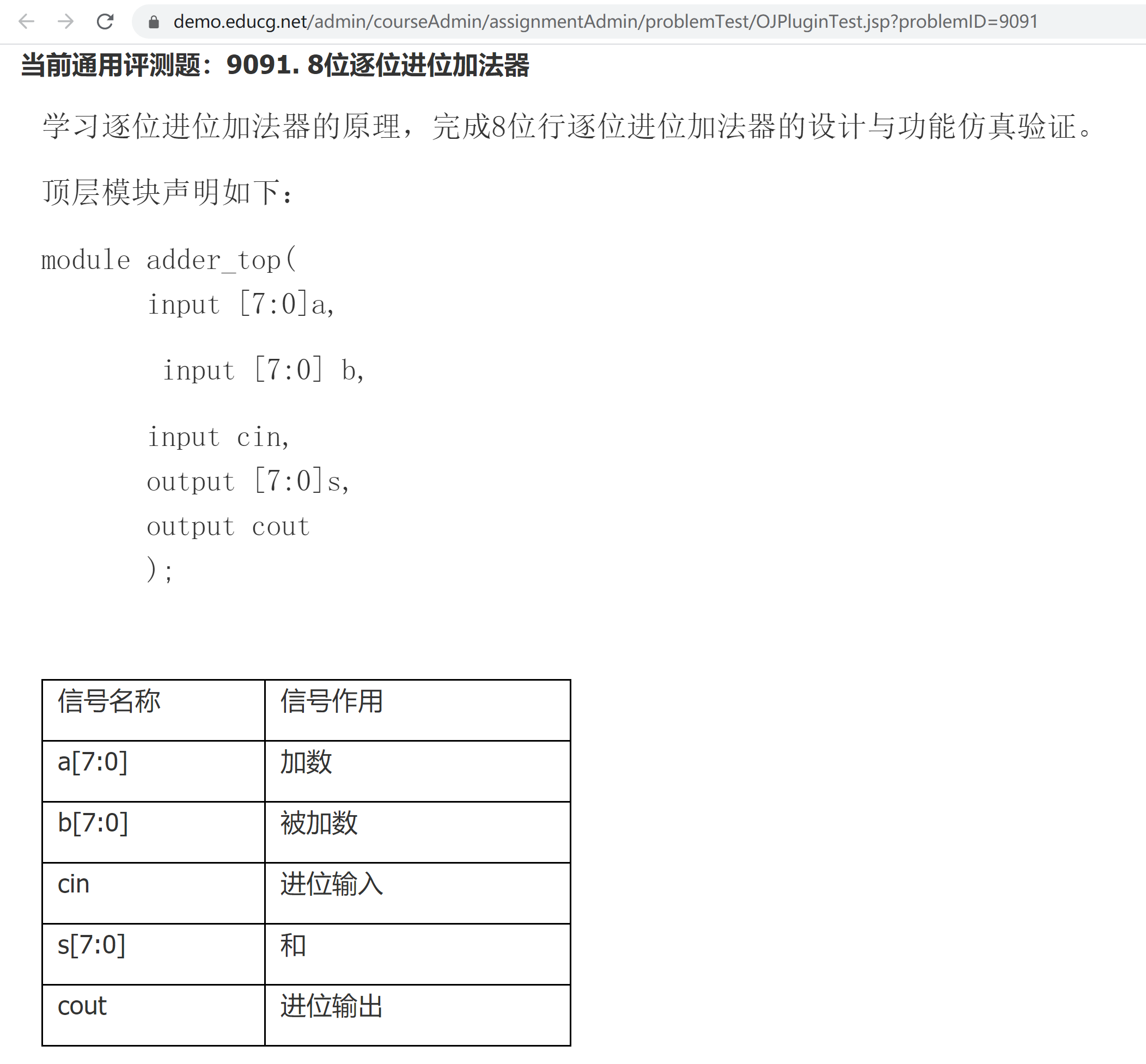

Verilog自动评测

学生根据题目要求,使用Verilog硬件描述语言实现特定功能的电路。仿真验证通过后,将Verilog源文件提交至希冀平台,由希冀平台的Verilog自动评测系统来评测学生所实现电路的功能是否正确。提供了配套的Verilog实验题库,包含Verilog语言基础题目、数字部件设计题目,以及CPU综合设计等实验题目。

●

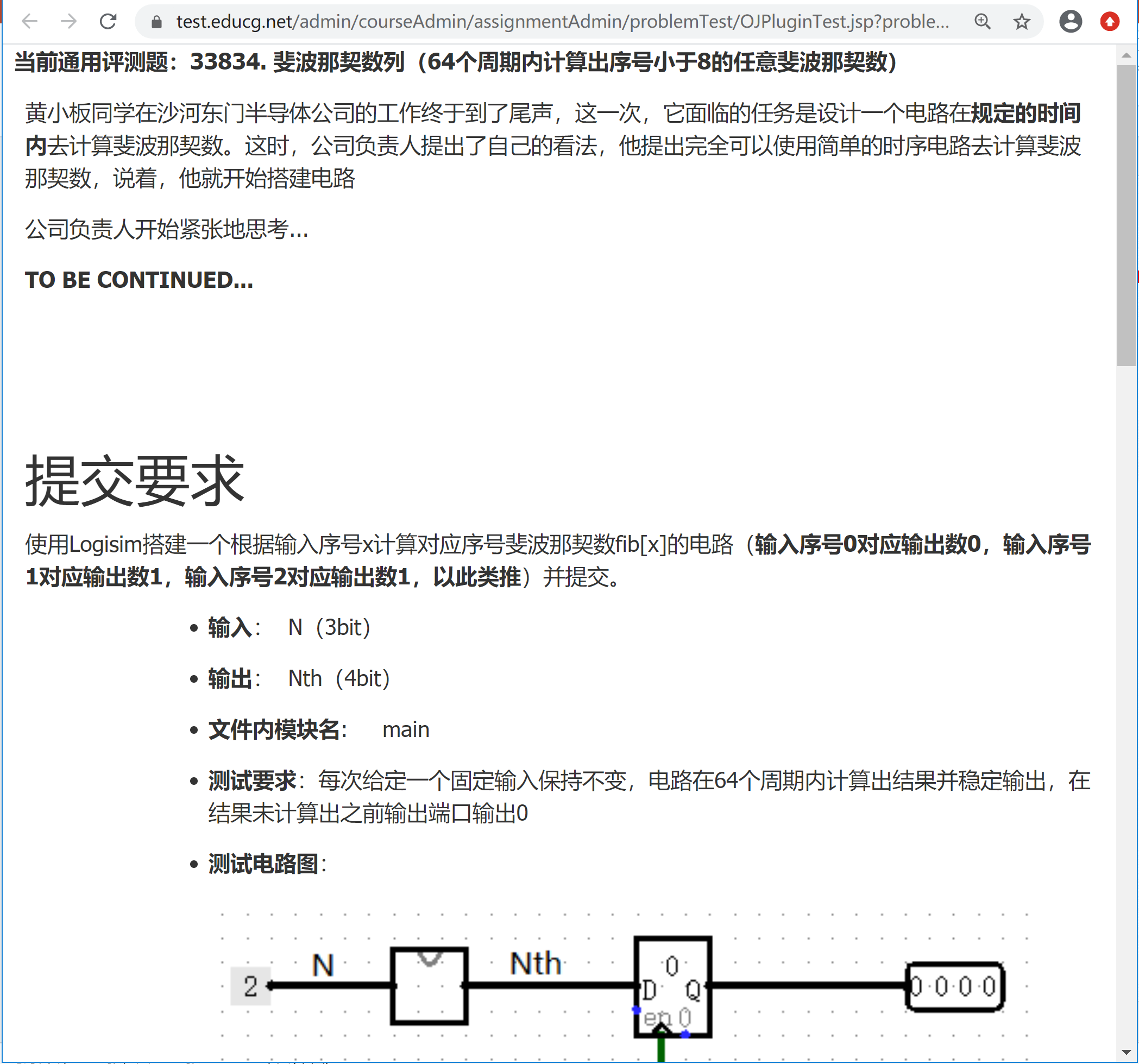

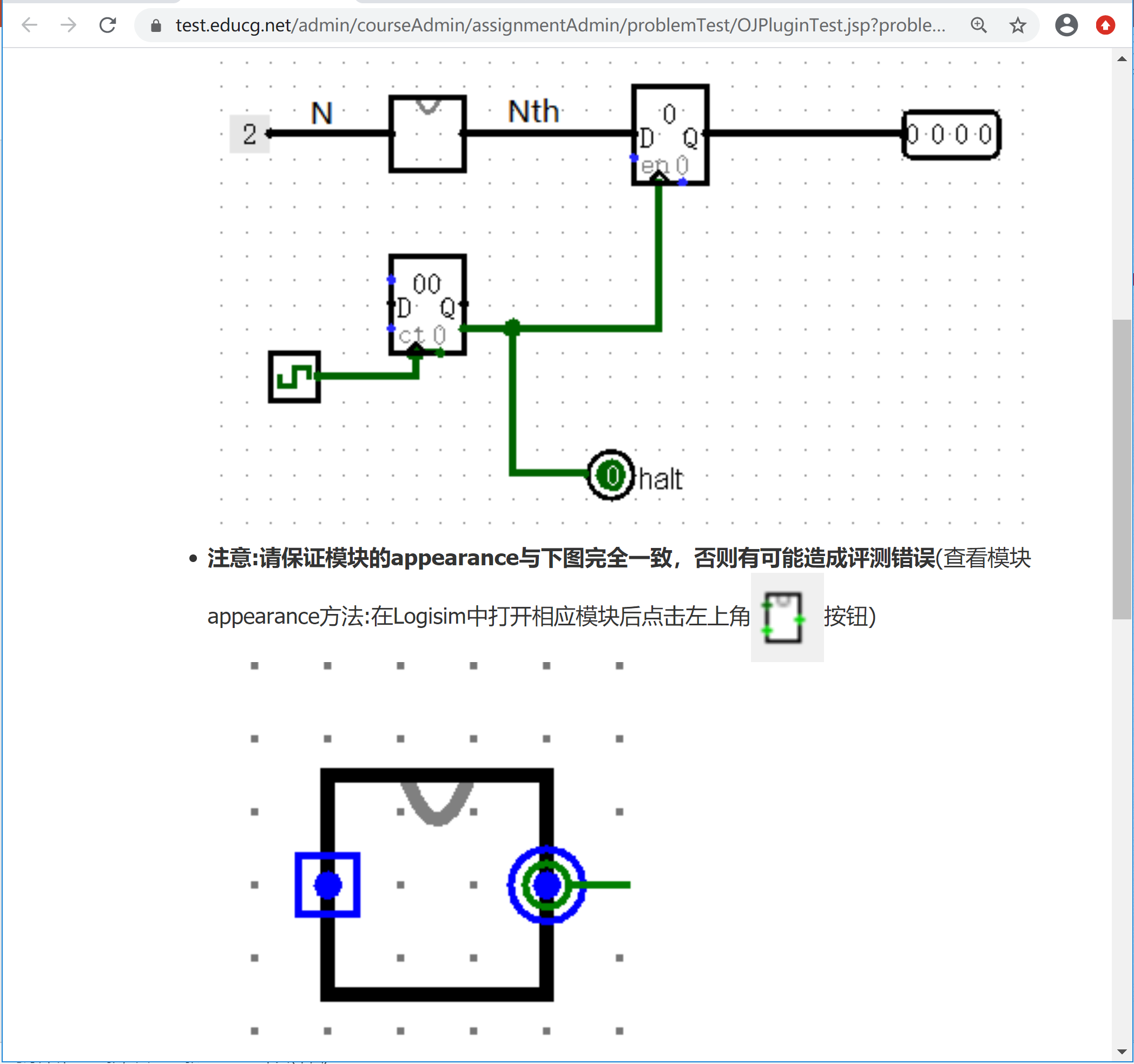

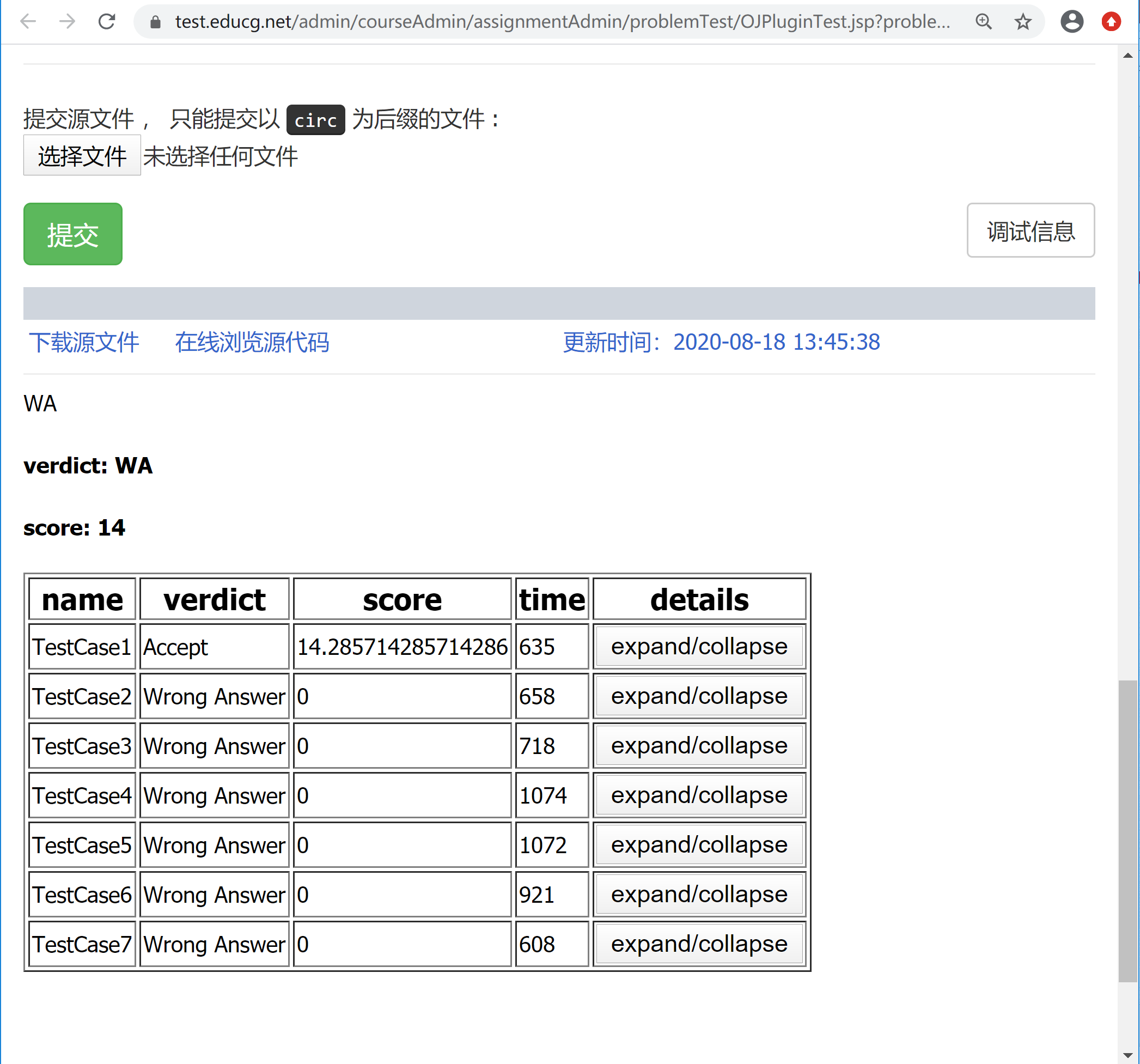

Logisim自动评测

学生根据题目要求,使用Logisim软件通过绘制电路图的方式实现特定功能的电路。仿真调试通过后,将Logisim电路源文件提交至希冀平台,由希冀平台的Logisim自动评测系统来评测学生所实现电路的功能是否正确。提供了配套的Logisim实验题库,包括特定功能电路设计题目和CPU综合设计题目。

●

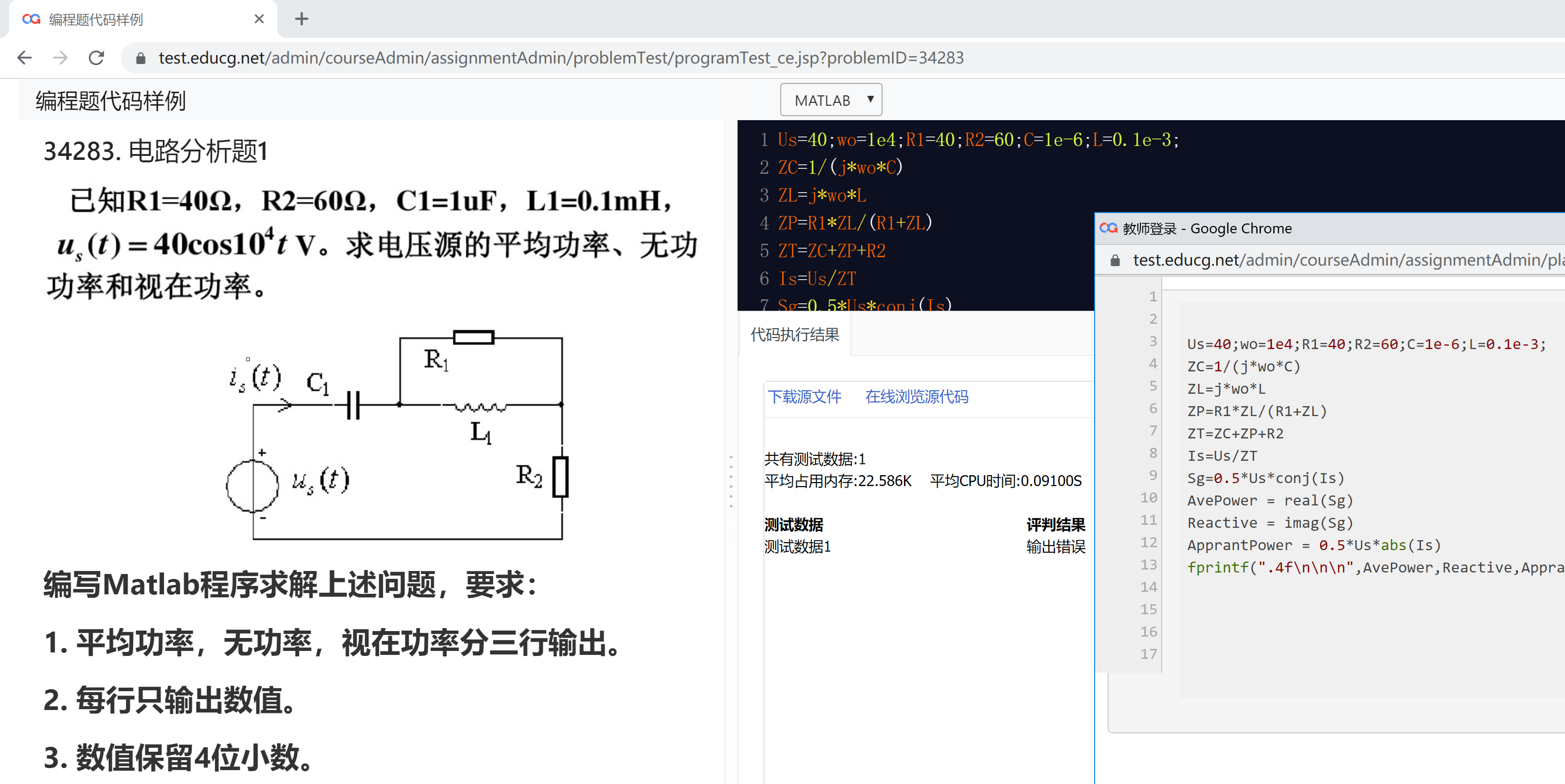

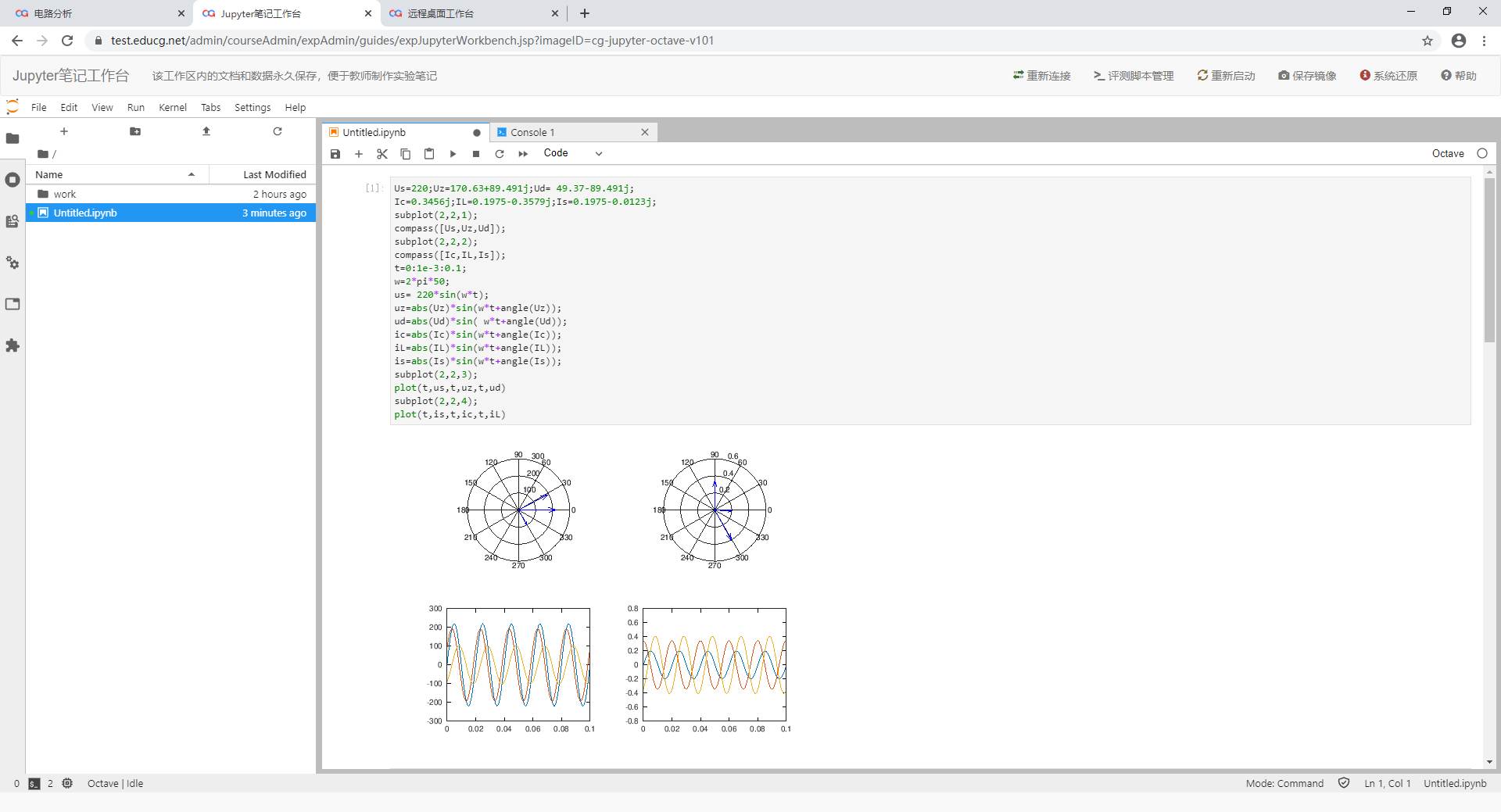

Matlab(Octave)自动评测

学生根据题目要求,使用Matlab语言编写程序分析电路特性,求解题目中给出的具体问题,例如求解视在功率、求解功率因数、绘制幅频特性图、绘制相频特性图等。Matlab代码编写调试完毕后,将程序提交至希冀平台,由希冀平台的Matlab自动评测系统评测学生所实现电路分析程序的功能和求解结果是否正确。Matlab自动评测系统提供了配套的电路分析实验题库。

●

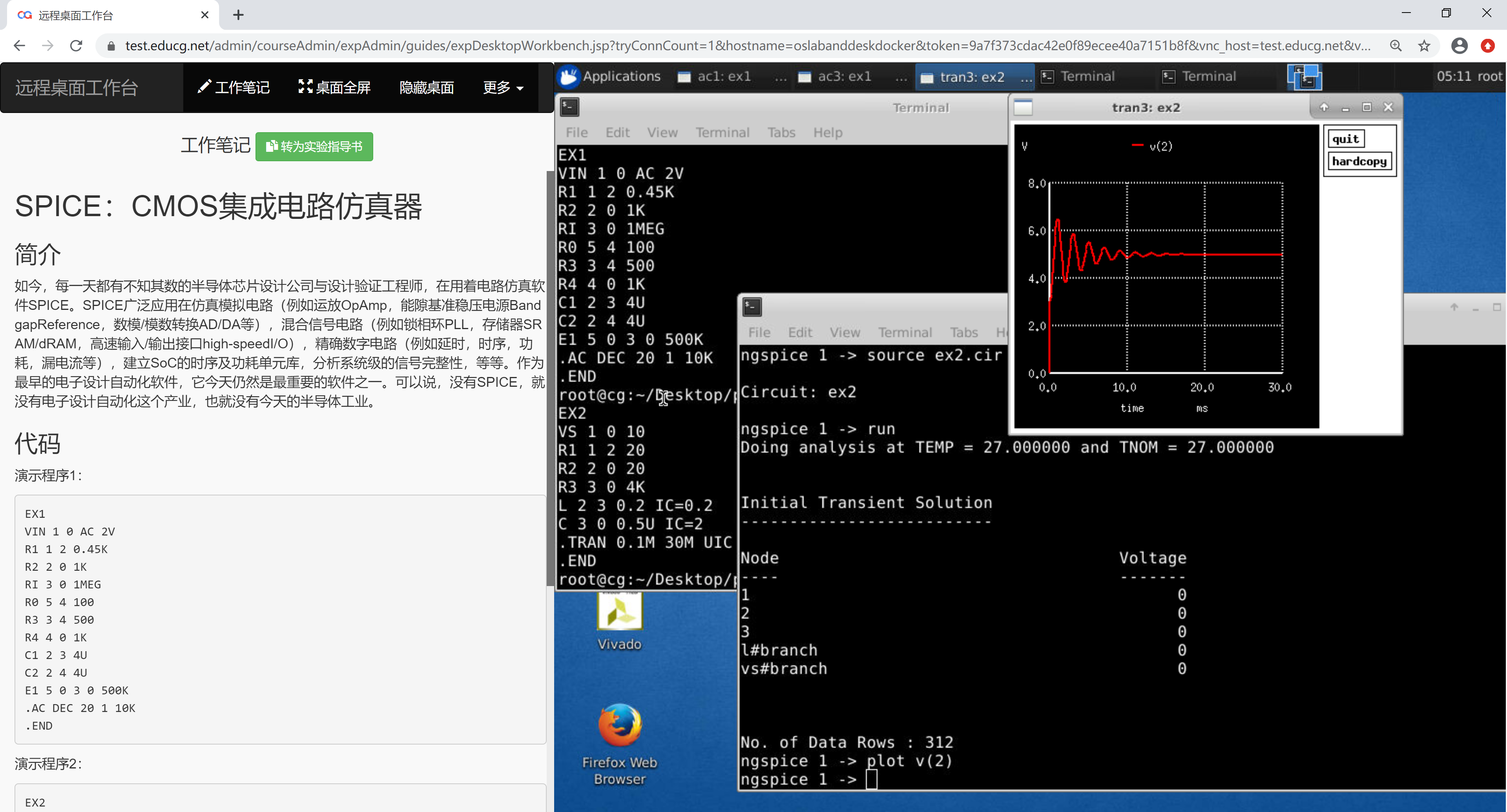

Spice自动评测

学生根据题目要求,使用Spice语言编写电路网表文件,求解题目中给出的具体问题,例如进行交流分析、绘制幅频特性图、求解幅值最大的频点等。网表文件编写调试完毕后,将该文件提交至希冀平台,由希冀平台的Spice自动评测系统评测学生所实现电路分析程序的功能和求解结果是否正确。Spice自动评测系统提供了配套的电路分析实验题库。

●

汇编语言自动评测

学生根据题目要求,使用NASM或者MARS编写汇编语言程序,求解题目中给出的具体问题。汇编代码编写调试完毕后,将汇编源程序提交至希冀平台,由希冀平台的汇编语言自动评测系统评测学生所实现程序的功能是否正确。汇编语言自动评测系统提供了配套的编程实验题库。

● C/C++程序自动化评测

详见希冀程序设计类课程教学系统。

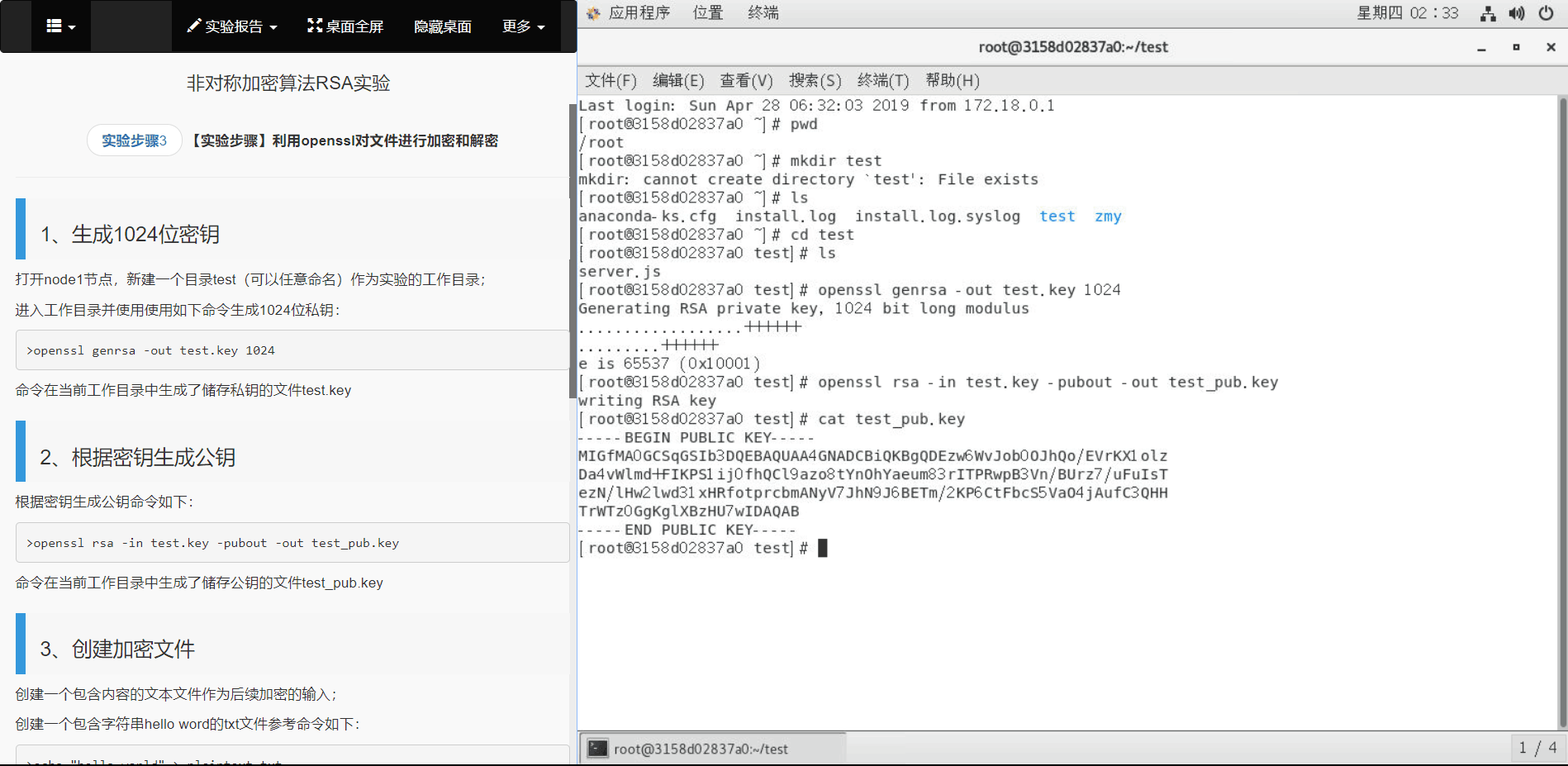

在线实验环境

● 随时随地在线实验

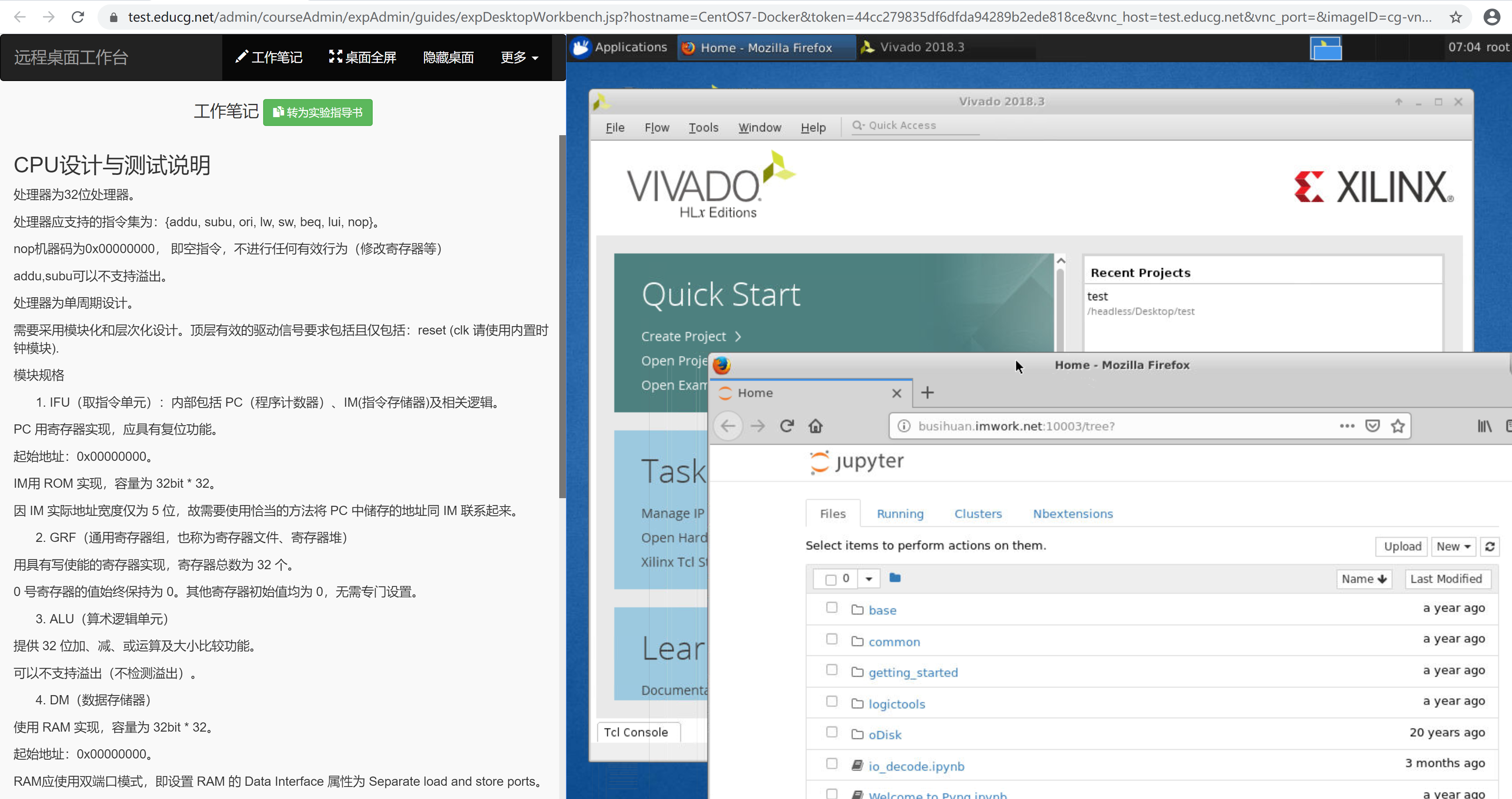

基于希冀云桌面实验平台,为学生提供了“开箱即用”的集成在线实验环境。实验页面分左右两栏,左栏为实验指导手册,右栏为云桌面实验环境。在云桌面实验环境内,安装了实验所需的各类软件,集成了各实验所需的实验支撑材料。

● 支持多种实验软件

通过希冀云桌面实验平台,针对各课程提供相应的实验软件在线实验环境,包括但不限于:

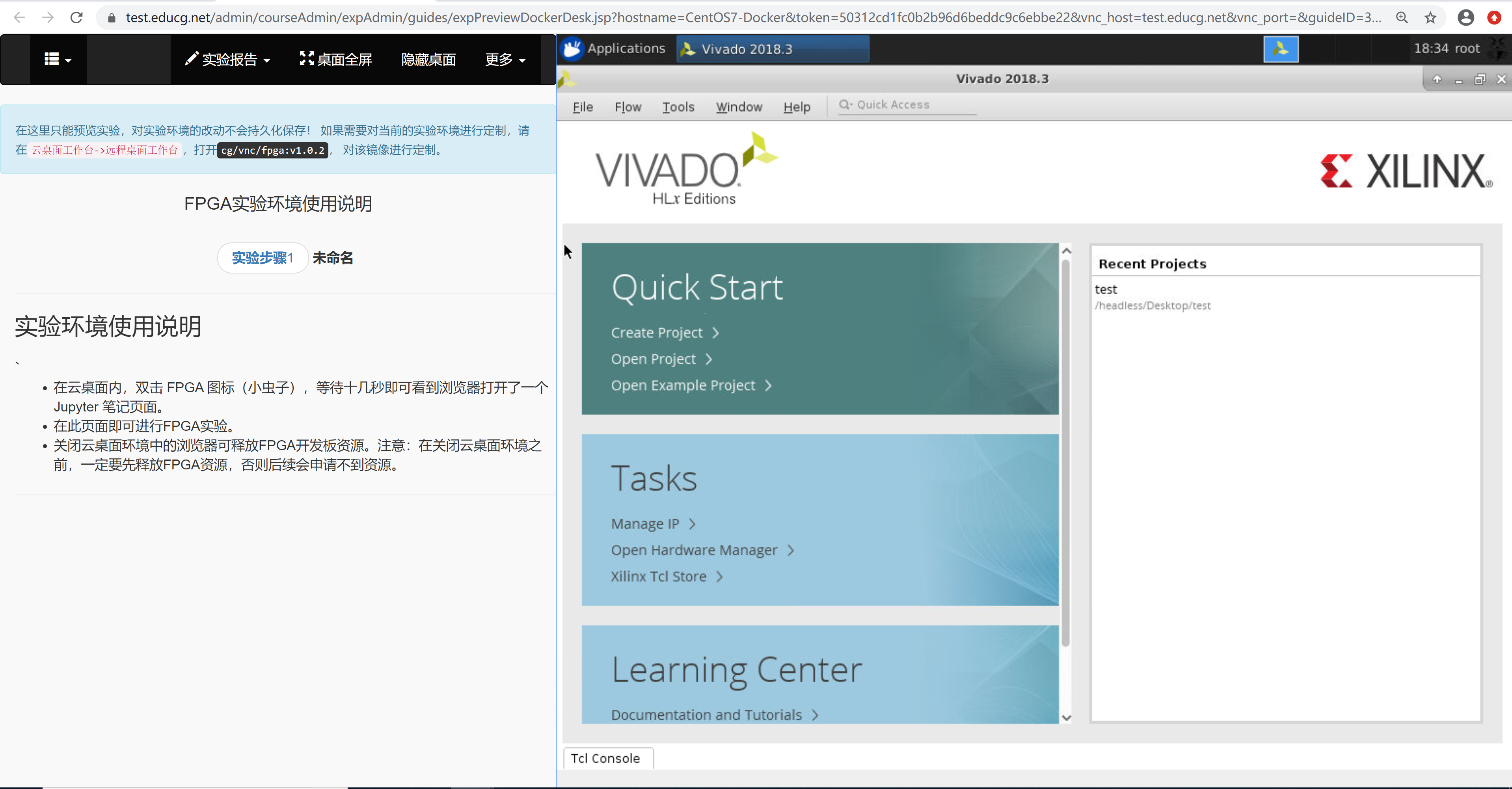

◼

Vivado,Vivado设计套件是FPGA厂商赛灵思公司2012年发布的集成设计环境,包括高度集成的设计环境和新一代从系统到IC级的工具。

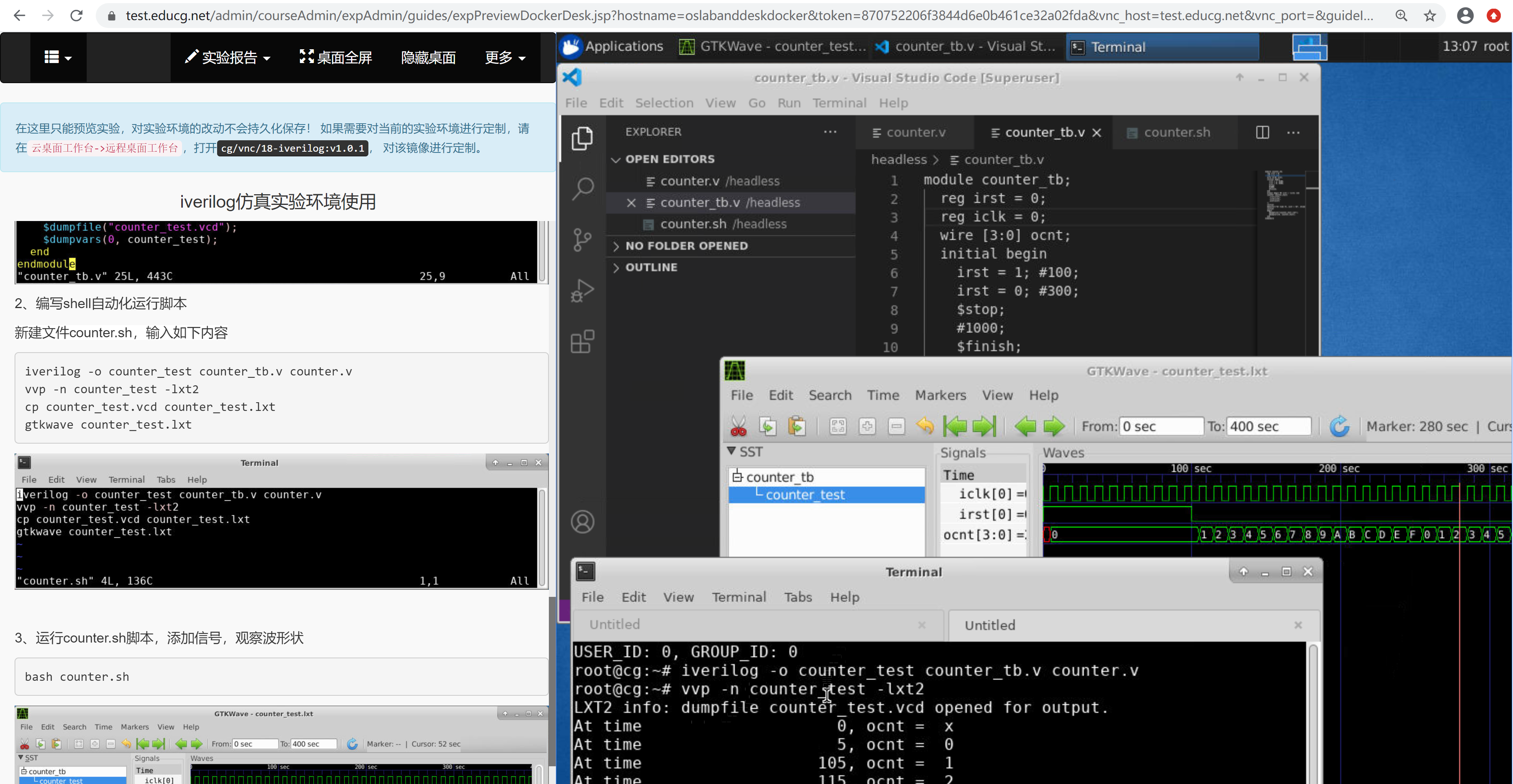

◼ Iverilog+GTKWave+VSCode,Icarus Verilog(Iverilog)是一个轻量、免费、开源的Verilog编译器,遵循 GNU GPL

license

许可证,支持Verilog/VHDL文件的编译和仿真,提供类似gcc的命令行操作方式。通过testbench文件可以生成对应的仿真波形数据文件,通过自带的GTKWave可查看仿真波形图。学生可以在VSCode中编写Verilog代码,使用Iverilog插件或者命令行方式编译仿真,通过GTKWave查看仿真波形图。

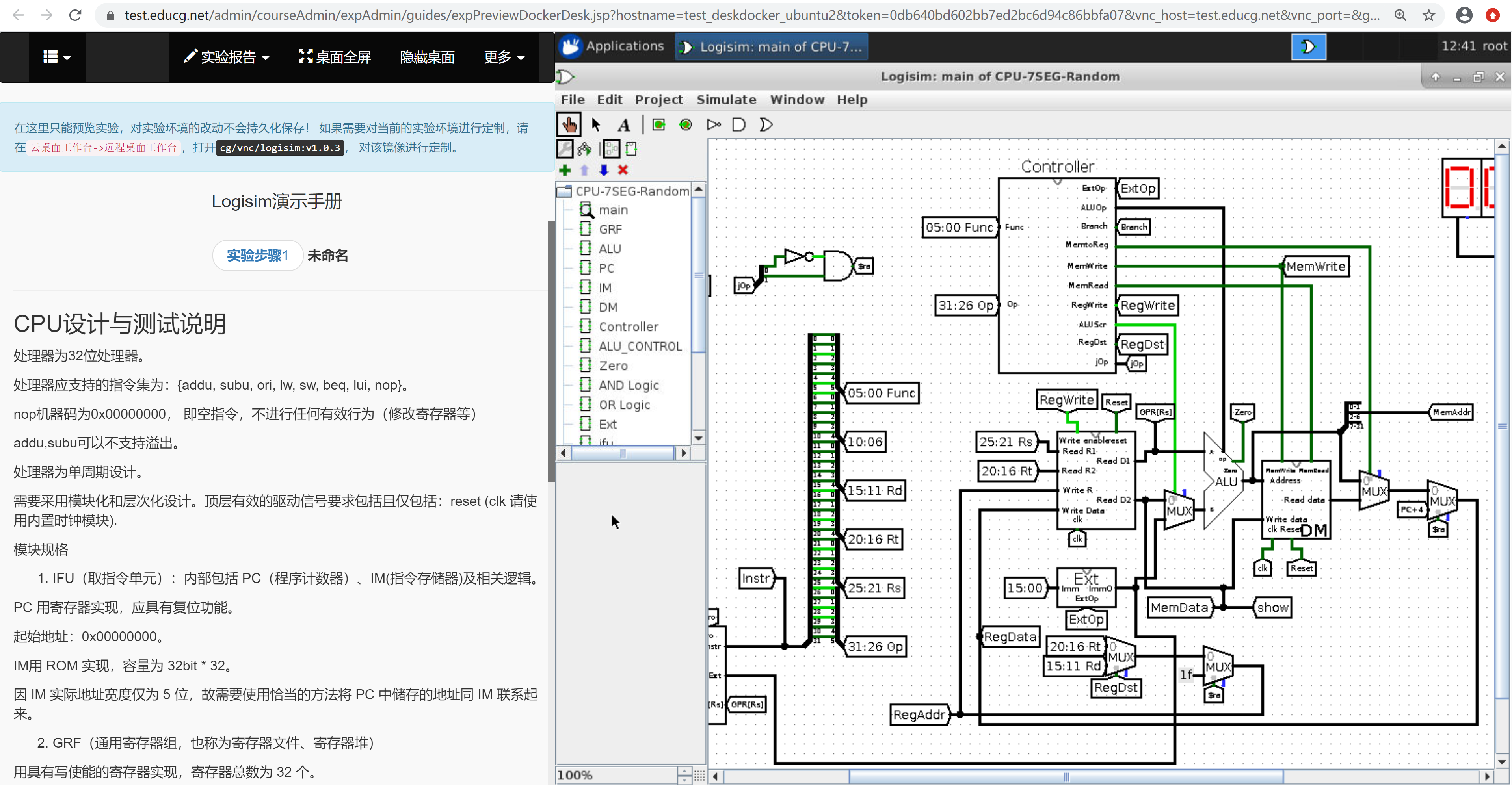

◼

Logisim,Logisim是一种用于设计和模拟数字逻辑电路的教学软件,具有界面简单、提供动态仿真等功能,有助于学生学习与逻辑电路相关的最基本概念。在Logisim中,学生能够以小规模子电路为基础逐步构建大规模数字集成电路,从而达到相关课程的实验教学目的。

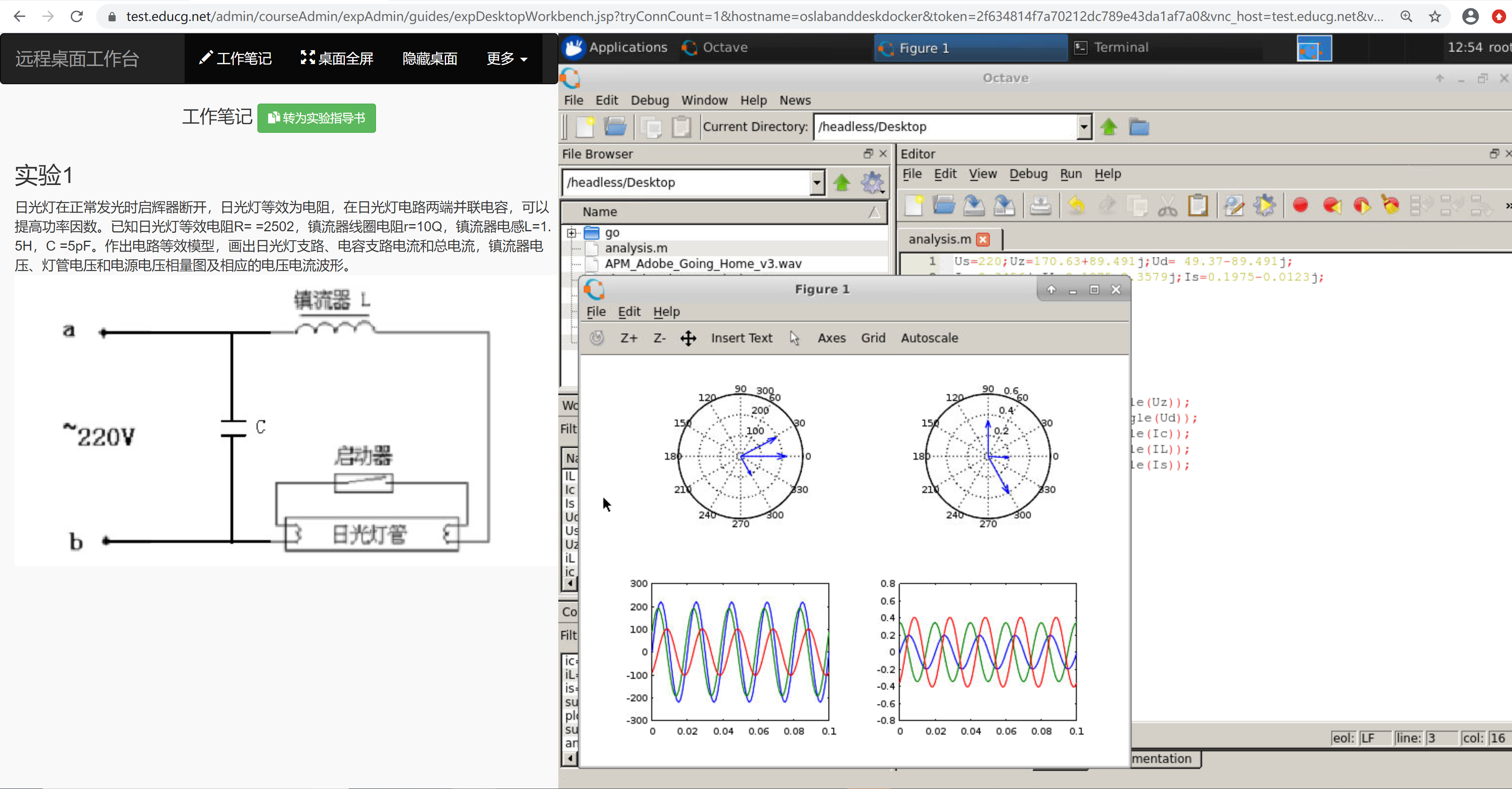

◼

Octave(Matlab),Octave为GNU项目下的开源软件,旨在解决线性和非线性的数值计算问题。该软件提供基于QT编写的GUI交互界面。Octave语法与Matlab语法非常接近,常被成称之为“开源的Matlab”,Matlab程序可以很容易移植到Octave。可以基于Octave的相关包开展电路分析、通信原理、高频电路等课程的实验。

◼ MARS,MARS

MIPS模拟器是MIPS处理器的汇编语言编辑器、汇编器、模拟器和调试器。MARS提供了一个轻量级的交互式集成开发环境(IDE),可用于开展MIPS汇编语言程序设计实验。

◼ NASM,x86平台上的汇编语言编译器,支持大量的文件格式,包括Linux,*BSD,a.out,ELF,COFF,Mach−O,Microsoft 16−bit

OBJ,Win32以及Win64,同时也支持简单的二进制文件生成。

◼

Spice,SPICE广泛应用在模拟电路仿真、混合信号电路、精确数字电路、SoC时序与功耗、系统级信号完整性分析等集成电路子领域。Spice是最早的电子设计自动化软件,在今天仍然是很重要的集成电路仿真软件。

FPGA云计算平台

●

支持私有云部署的FPGA云计算平台

通过将多块FPGA开发板高密度封装于标准化机箱中,可安装交付到高校实验室中,实现私有云部署。

●

与希冀云桌面实验环境无缝融合

学生在云桌面内可通过双击FPGA桌面图标,即可分配到一块FPGA硬件开发板。在做实验的过程中,学生对分配的开发板是独占的。

● 支持交互式使用远程硬件开发板

通过Jupyter

Notebook连接远程开发板,使用Python程序交互式加载和运行比特流文件。比特流文件在FPGA上的运行结果可通过文本或者波形图的方式显示。

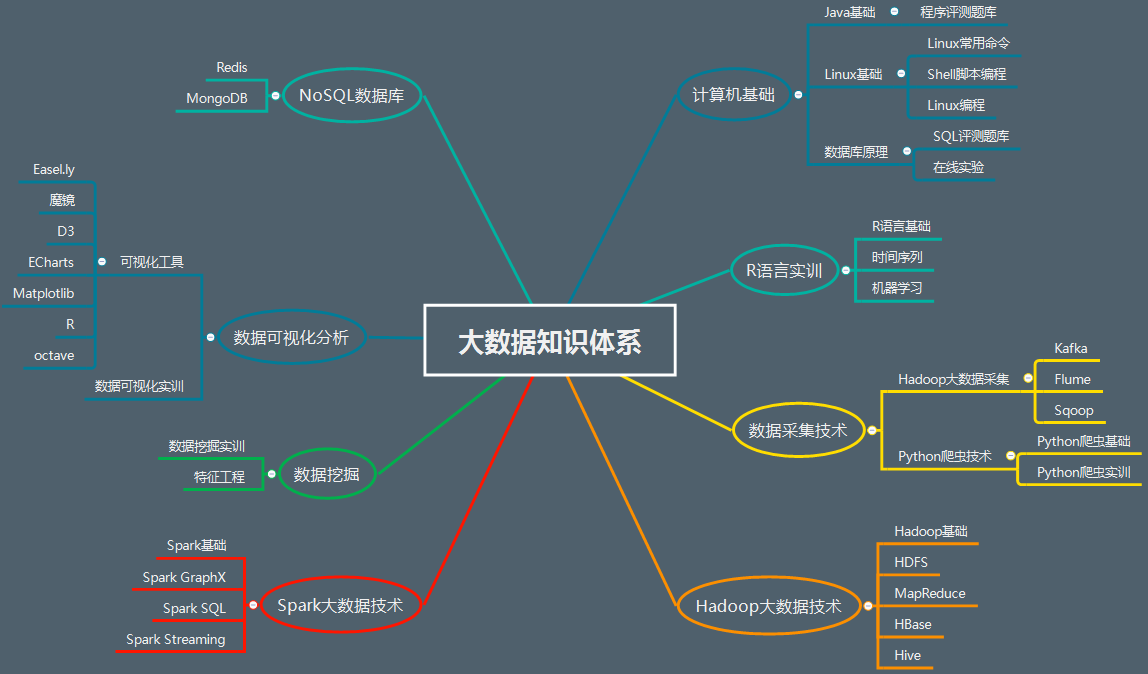

课程实验体系

面向提升集成电路专业学生工程实践能力的实验体系,提供多门实验课程,包括但不限于:

| 课程列表 点击课程名称,可以查看对应的实验列表 | |

| ● Verilog硬件描述语言 | ● 数字电路 |

| ● 计算机组成原理 | ● 处理器设计 |

| ● 智能处理器设计 | ● 汇编语言程序设计 |

| ● 电路分析 | ● FPGA技术 |

| ● VLSI数字信号处理 | ● VLSI数字通信原理与设计 |

| ● 数字集成电路设计 | ● CMOS模拟集成电路设计 |

| ... | ... |