围绕系统能力培养,构造递进式实验体系

- 基于B/S架构的自动评测系统

-

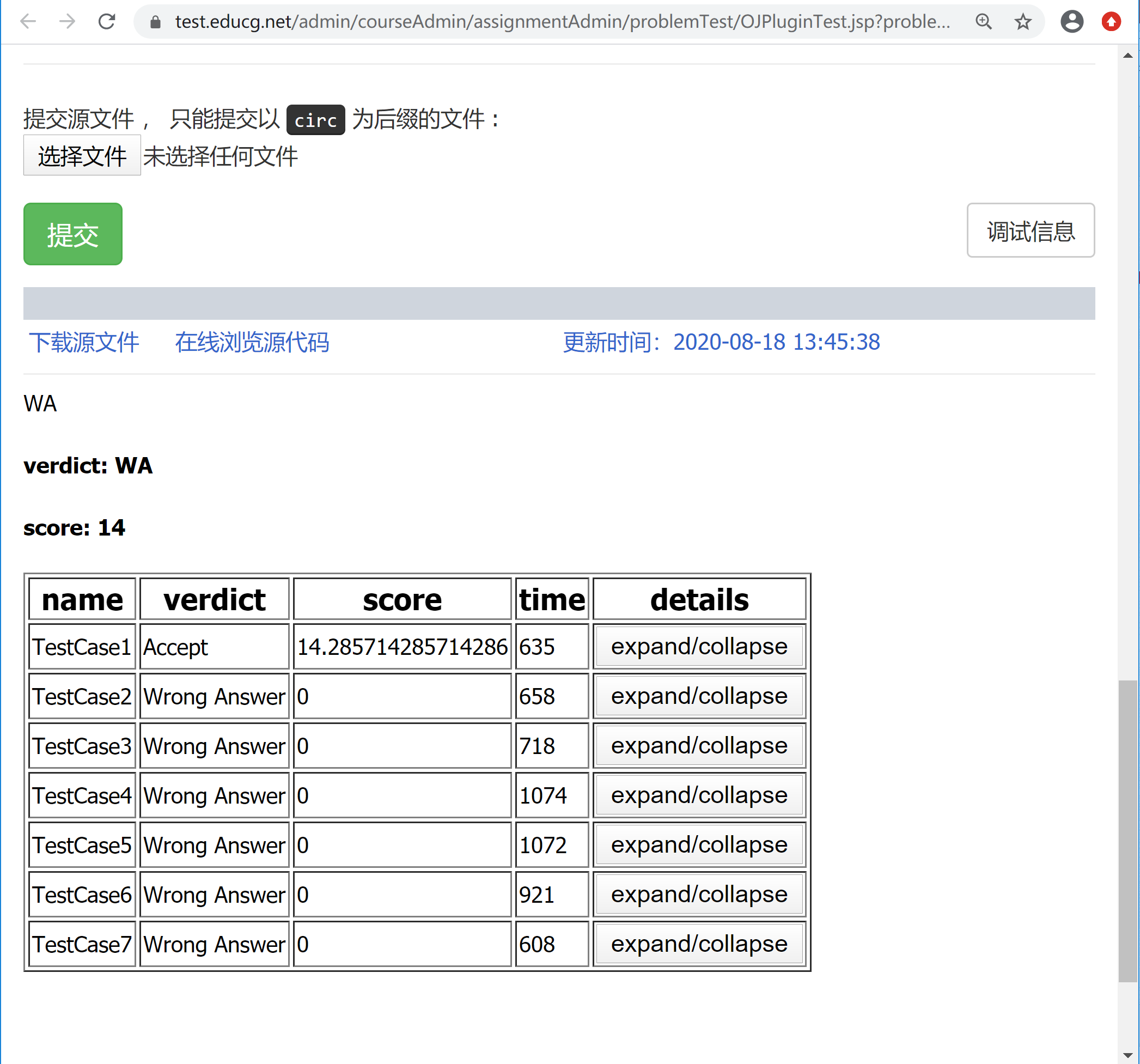

自动化评价学生提交的实验代码。在线自动化测试使得严谨完善的测试成为可能,同时测试结果的统计分析有力支撑了教学设计改进。

- 计算机组成实验体系

-

涵盖3大类实验:数字逻辑、汇编语言、计算机组成。

语言/工具:MIPS汇编/Verilog、Logisim、MARS、ISE。

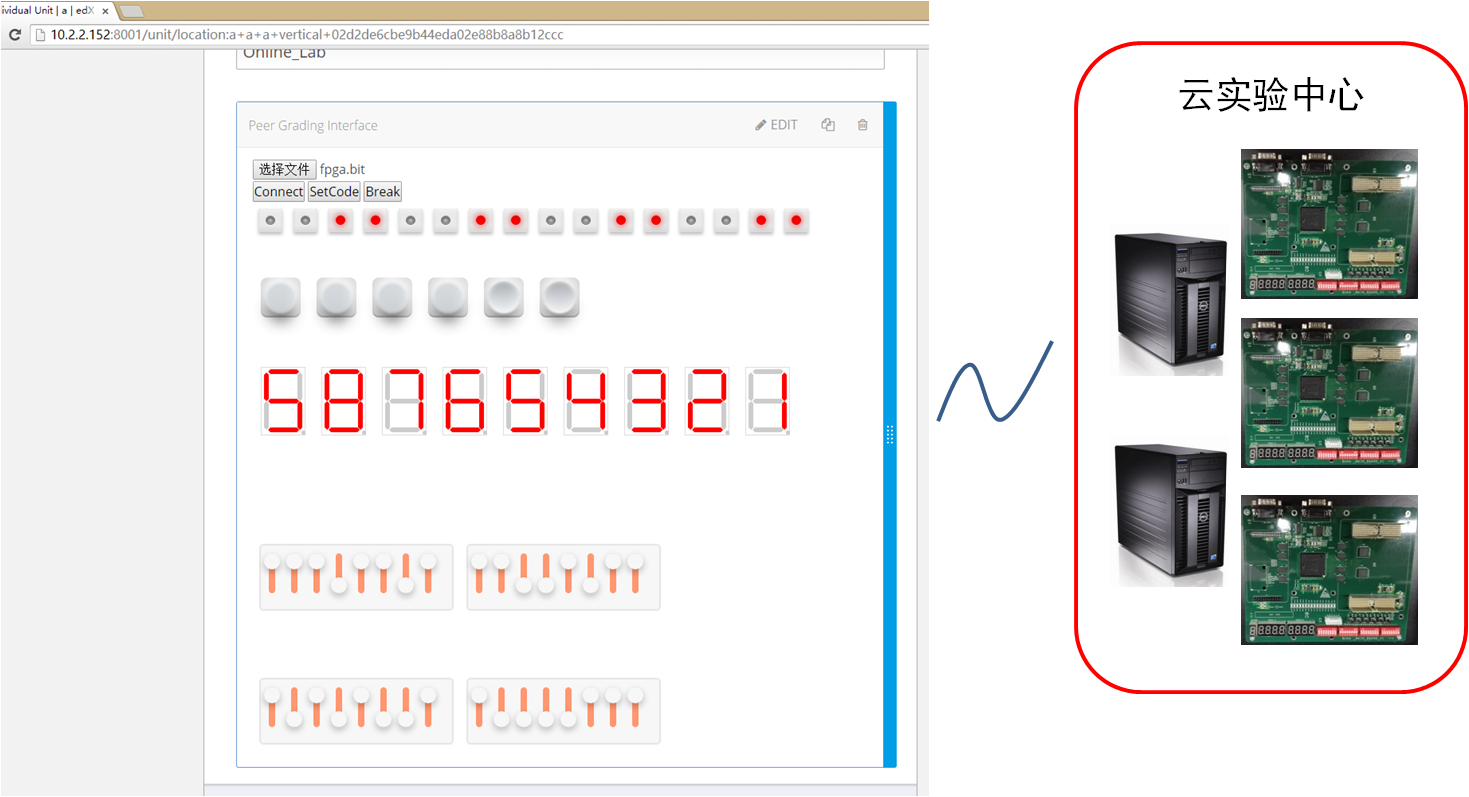

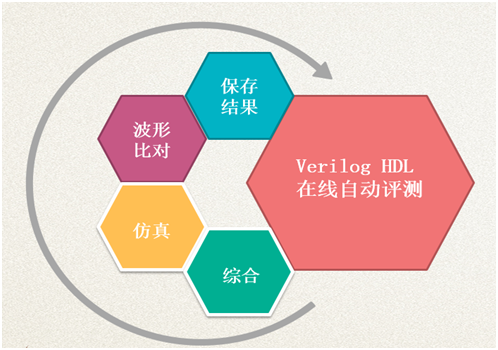

Verilog HDL自动评测

- Verilog HDL代码的在线自动评测

-

无须教师验收,自行记录VerilogHDL代码评测结果。

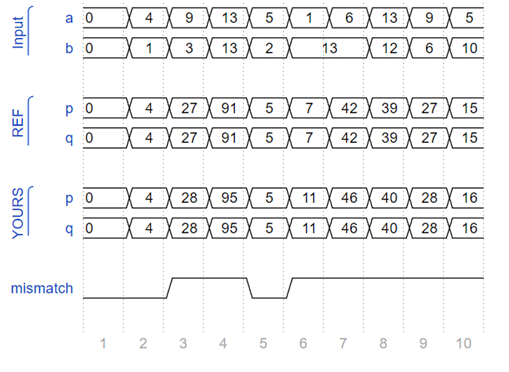

- 支持Verilog HDL在线综合仿真

-

仿真波形展示,mismatch变量使得对错一目了然。

综合仿真结果输出较本地EDA平台更快。 返回综合后的标准输出,便于展开调试

Logisim在线实验

- Logisim自动评测

-

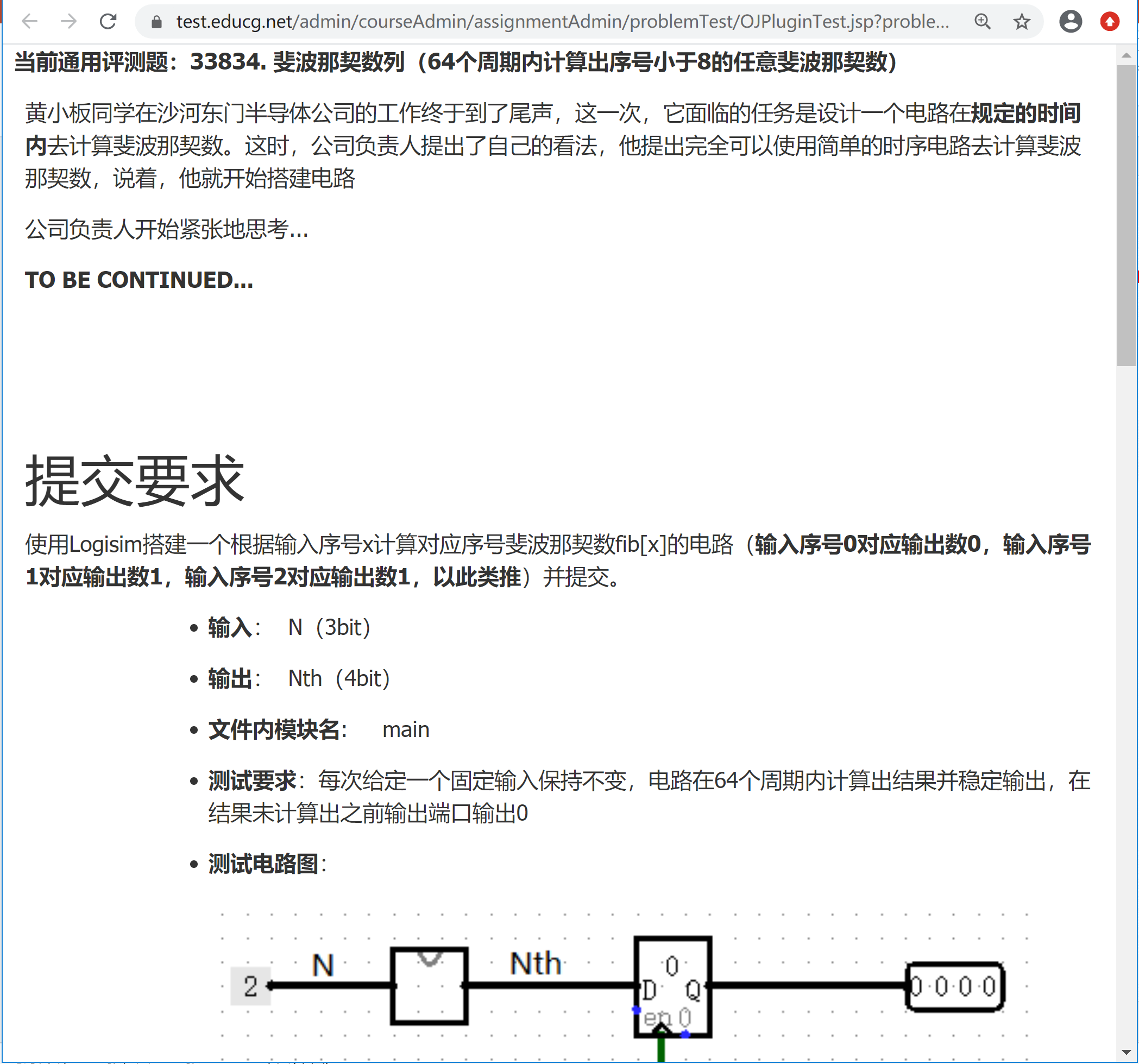

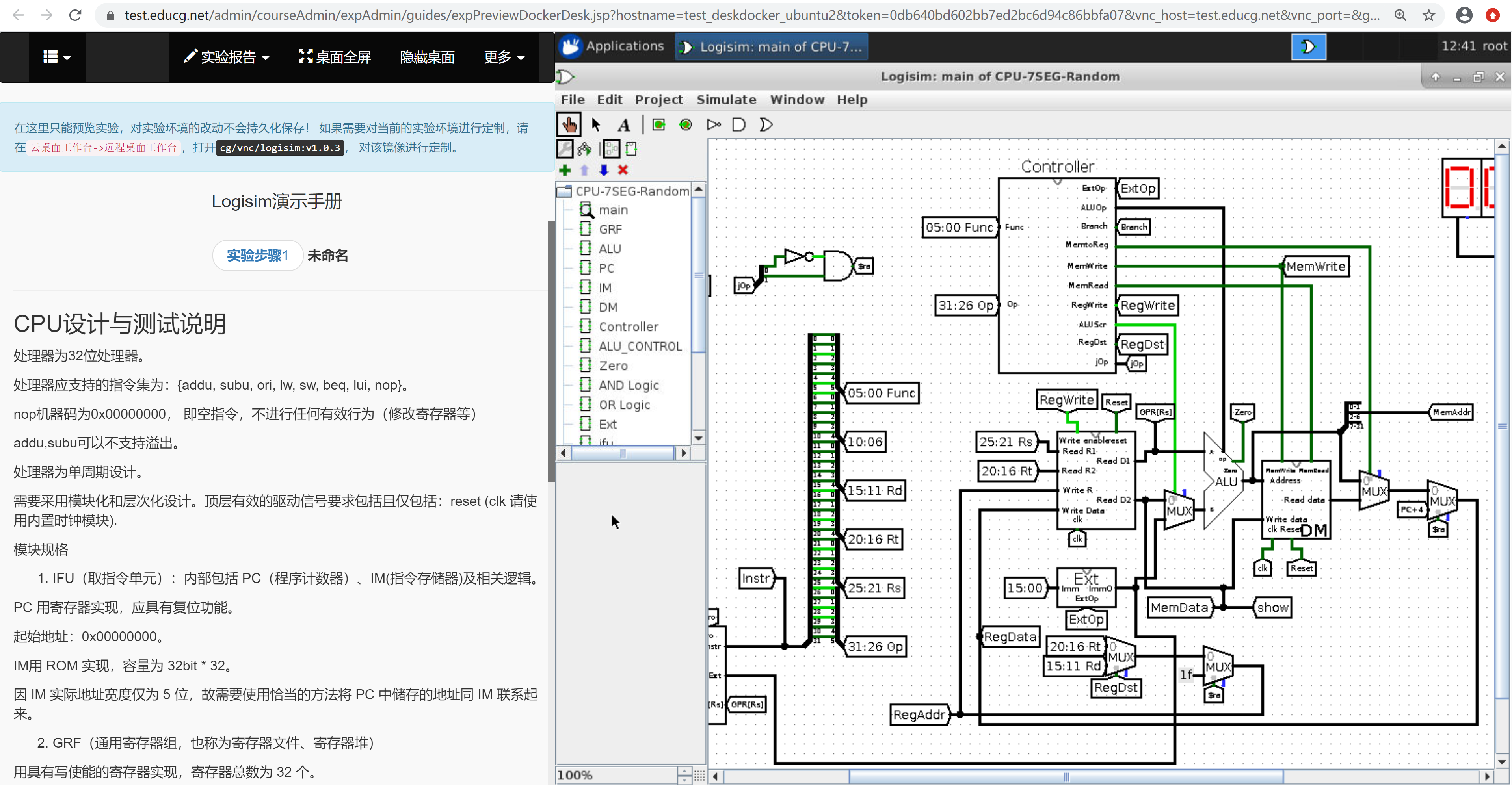

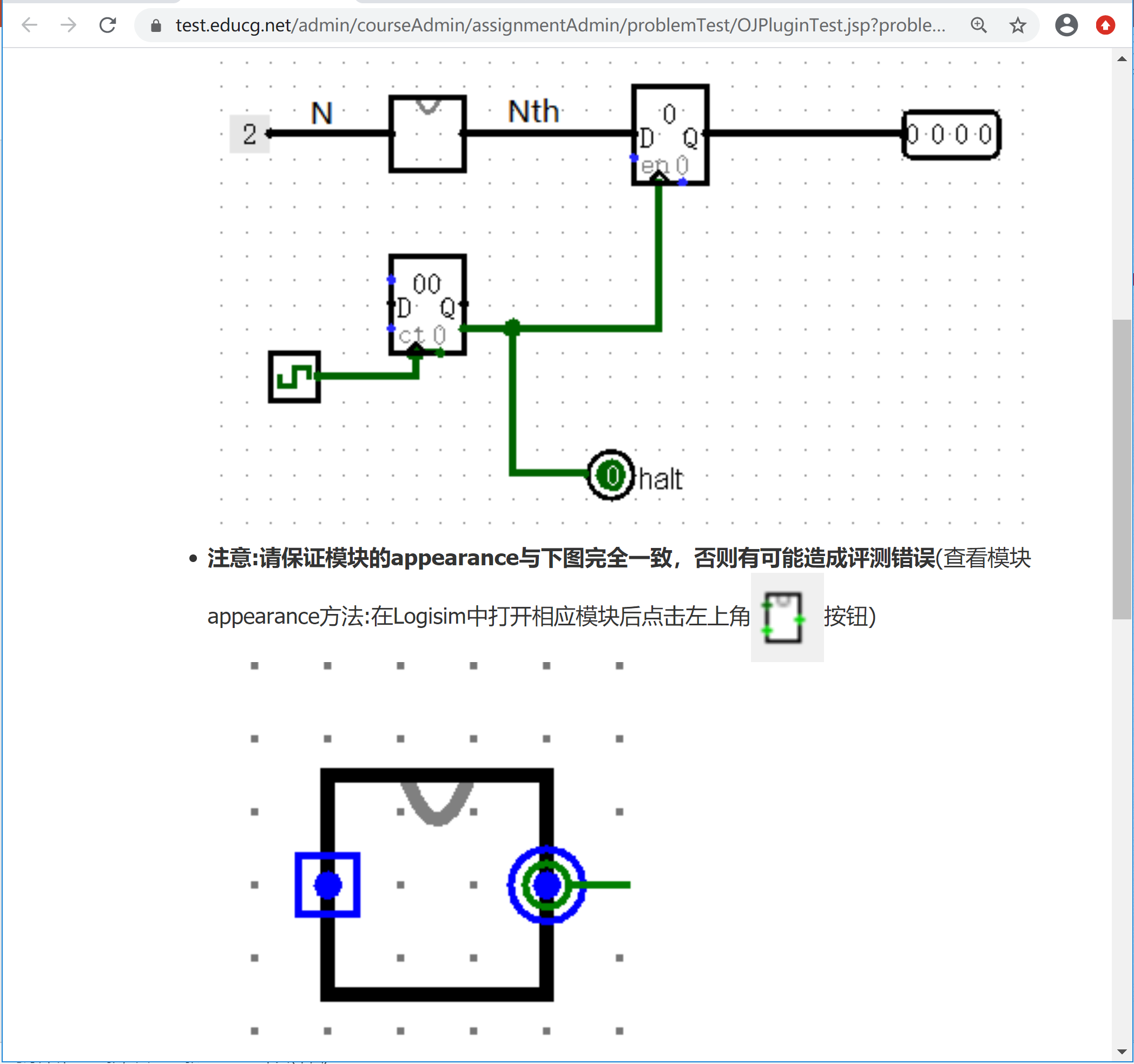

学生根据题目要求,使用Logisim软件通过绘制电路图的方式实现特定功能的电路。仿真调试通过后,将Logisim电路源文件提交至希冀平台,由希冀平台的Verilog自动评测系统来评测学生所实现电路的功能是否正确。提供了配套的Logisim实验题库,包括特定功能电路设计题目和CPU综合设计题目。

- Logisim在线仿真

-

Logisim是一种用于设计和模拟数字逻辑电路的教学软件,具有界面简单、提供动态仿真等功能,有助于学生学习与逻辑电路相关的最基本概念。在Logisim中,学生能够以小规模子电路为基础逐步构建大规模数字集成电路,从而达到相关课程的实验教学目的。

FPGA云计算平台

●

支持私有云部署的FPGA云计算平台

通过将多块FPGA开发板高密度封装于标准化机箱中,可安装交付到高校实验室中,实现私有云部署。

●

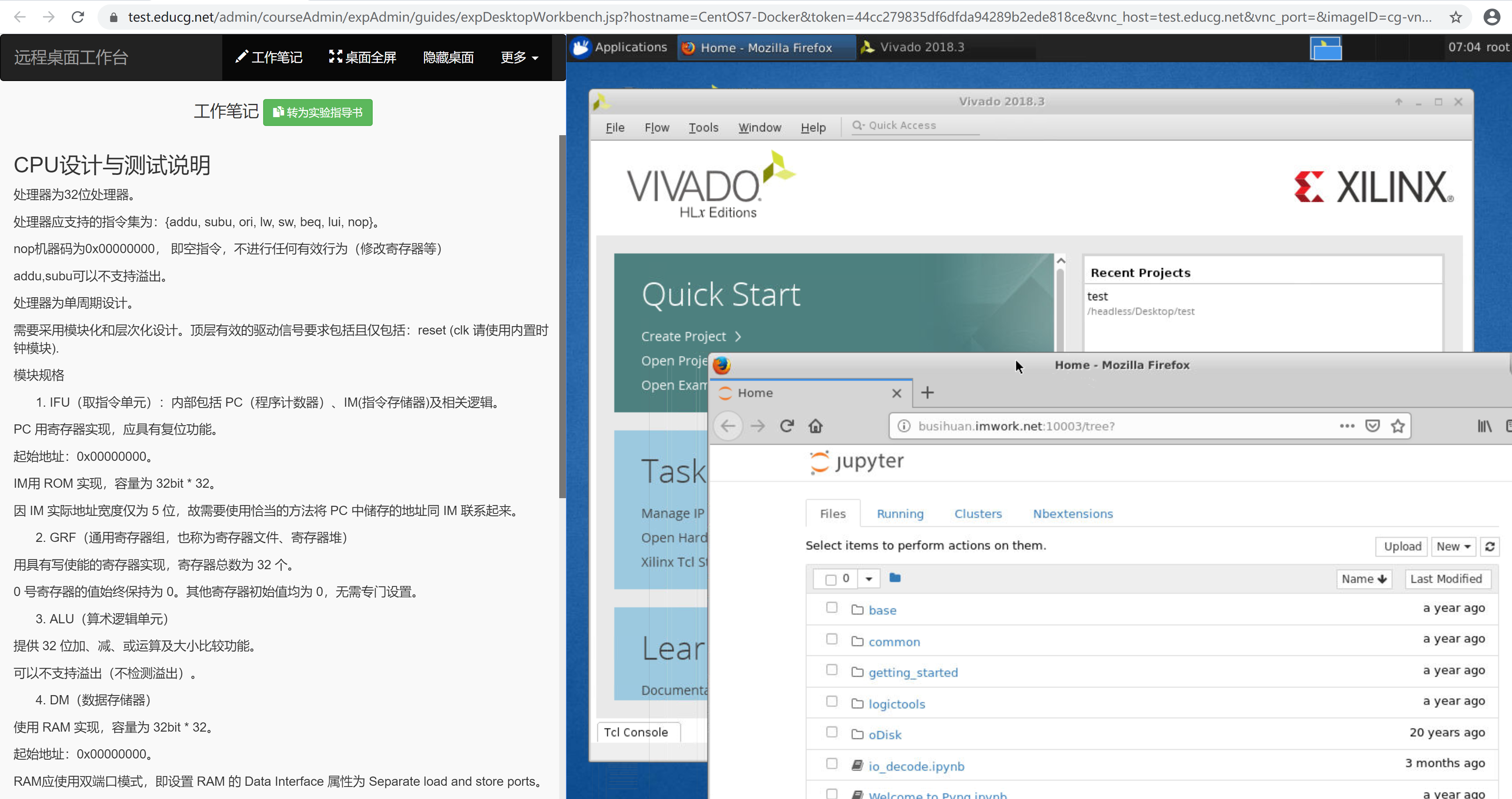

与希冀云桌面实验环境无缝融合

学生在云桌面内可通过双击FPGA桌面图标,即可分配到一块FPGA硬件开发板。在做实验的过程中,学生对分配的开发板是独占的。

● 支持交互式使用远程硬件开发板

通过Jupyter

Notebook连接远程开发板,使用Python程序交互式加载和运行比特流文件。比特流文件在FPGA上的运行结果可通过文本或者波形图的方式显示。

高质量的数字系统设计实验体系

- 数字系统设计基本能力训练

-

基本能力训练包括从Verilog语言的基本特征认识到组合逻辑、时序逻辑电路的原理图与Verilog语言的对应练习,从读懂仿真波形的练习到学会写仿真测试模块。提供了较为完整的数字系统基本能力的训练练习。

- 数字逻辑实验

-

数字逻辑实验涵盖了从组合逻辑到时序逻辑、状态机设计的完整实验体系,按照数字系统认知过程分为四个大实验:组合逻辑实验、时序逻辑实验、状态机实验以及复杂数字系统设计实验,满足多层次数字系统设计要求。

- 计算机组成原理实验

-

采用分模块设计原则,设计了6个相互关联的计算机组成原理实验,学生可以从简单到复杂,最终构造出一个相对完整的CPU。 每个实验都设置多个不同难度级别的挑战性任务,并自动评测,节省教师工作量的同时,让学生获得数字系统开发的成就感。

|-基本能力训练/

| |--VerilogHDL语言/

| | |--基本练习/

| | | |--单个wire

| | | |--四位wire

| | | |--反相器

| | | |--与门

| | | |--或非门

| | | |--异或门

| | | |--wire的声明

| | |--向量练习/

| | | |--向量基础

| | |--模块练习:层次/

| | | |--位置连接端口

| | | |--名字连接端口

| | | |--多个模块

| | | |--加法减法器

| | |--过程练习/

| | | |--always块(组合逻辑)

| | | |--always块(时序逻辑)

| | | |--if 语句

| | | |--case语句

| | | |--避免锁存器产生

| | |--Verilog其它特征/

| | | |--三目运算符

| | | |--减操作符

| |--电路/

| | |--组合逻辑/

| | | |--基本门电路

| | | |--多路选择器

| | | |--运算电路

| | | |--由卡诺图到电路

| | |--时序逻辑/

| | | |--锁存器和D触发器

| | | |--计数器

| | | |--移位寄存器

| | | |--更多电路

| | | |--有限状态机

| | |--更复杂电路/

| | | |--1000位进1计数器

| | | |--有限状态机:带使能的移位寄存器

| |--验证:读懂仿真/

| | |--找到代码中的bug/

| | | |--多路选择器

| | | |--与非电路

| | | |--加减法电路

| | | |--case语句电路

| | |--从仿真波形建立电路/

| | | |--组合逻辑电路/

| | | |--时序逻辑电路/

| |--验证:写teatbench/

| | |--周期性时钟产生电路

| | |--与门测试电路

|

|-数字逻辑实验/

| |--组合逻辑设计/

| | |--四位乘法器

| | |--八位乘法器

| | |--四位除法器

| | |--八位乘法器

| | |--八位逐位进位加法器

| | |--八位超前进位加法器

| | |--八位选择进位加法器

| |--时序逻辑设计/

| | |--完成在七段数码管上滚动显示学号

| | |--按键输入学号,并循环显示

| | |--SRAM芯片数据存取

| |--状态机练习/

| | |--验证1101序列(Mealy型)

| | |--验证1101序列(Moore型)

| | |--验证1000序列

| | |--电梯控制器

| |--复杂数字系统设计/

| | |--简单处理器的ASM设计

| | |--流水线乘法器设计

|

|-计算机组成原理实验/

| |--取指模块设计

| |--寄存器堆设计

| |--存储单元设计

| |--算术逻辑单元设计

| |--控制器设计

| |--完整CPU设计

计算机组成实验资源

| 实验类别 | 实验列表 | 实验工具 | 自动评测 |

|---|---|---|---|

数字逻辑 |

swap电路(组合逻辑) | Logisim | |

| 排序电路(基于swap电路搭建) | Logisim | ||

| 求解多元线性回归问题 | Logisim | ||

| 2^n mod 5(移位取模,时序逻辑) | Logisim | ||

| 斐波那契数列(64个周期内计算出序号小于8的任意斐波那契数) | Logisim | ||

| 斐波那契数列-挑战(64个周期内计算出序号小于2^32的任意斐波那契数) | Logisim | ||

| CRC校验码计算 | Logisim | ||

| 字符自动机(正则表达式匹配) | Logisim | ||

| 字符自动机(正则表达式匹配并计数) | Logisim | ||

| 计数器 | Verilog | ||

| 字符自动机(正则表达式匹配) | Verilog | ||

| 格雷码计数器 | Verilog | ||

| 表达式状态机(表达式校验) | Verilog | ||

| 表达式状态机-允许括号(表达式校验) | Verilog | ||

汇编程序 |

判断闰年 | MARS | |

| 稀疏矩阵转三元组 | MARS | ||

| 哈密顿回路(递归) | MARS | ||

| 矩阵乘法 | MARS | ||

| 选择排序 | MARS | ||

| 回文串判断 | MARS | ||

| 全排列 | MARS | ||

| 字符统计 | MARS | ||

| 矩阵的2^n次幂 | MARS | ||

| 0-1迷宫(深度优先遍历) | MARS | ||

| 矩阵转置相加 | MARS | ||

| 倒序全排列 | MARS | ||

| 计数排序 | MARS | ||

数字部件 |

4位全加器 | Logisim | |

| 4位比较器 | Logisim | ||

| 4位ALU | Logisim | ||

| 4位加法器 | Verilog | ||

| 32位六运算ALU | Verilog | ||

CPU |

单周期CPU (logisim) | Logisim | |

| 单周期CPU | Verilog | ||

| 多周期CPU(1) | Verilog | ||

| 多周期CPU(2) | Verilog |