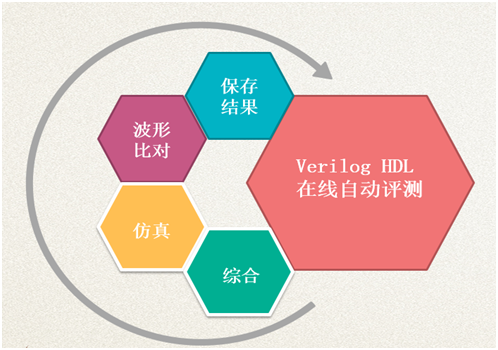

支持Verilog HDL自动评测的数字系统设计在线实验平台

平台特色

无须教师验收,自行记录VerilogHDL代码评测结果。

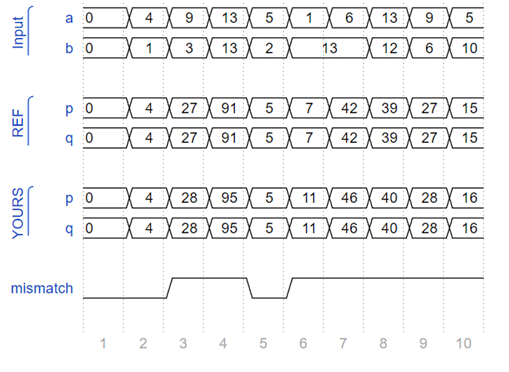

仿真波形展示,mismatch变量使得对错一目了然。

综合仿真结果输出较本地EDA平台更快。 返回综合后的标准输出,便于展开调试

完善的高质量的数字系统设计相关教学资源

- 数字系统设计基本能力训练

-

基本能力训练包括从Verilog语言的基本特征认识到组合逻辑、时序逻辑电路的原理图与Verilog语言的对应练习,从读懂仿真波形的练习到学会写仿真测试模块。提供了较为完整的数字系统基本能力的训练练习。

- 数字逻辑实验

-

数字逻辑实验涵盖了从组合逻辑到时序逻辑、状态机设计的完整实验体系,按照数字系统认知过程分为四个大实验:组合逻辑实验、时序逻辑实验、状态机实验以及复杂数字系统设计实验,满足多层次数字系统设计要求。

- 计算机组成原理实验

-

采用分模块设计原则,设计了6个相互关联的计算机组成原理实验,学生可以从简单到复杂,最终构造出一个相对完整的CPU。 每个实验都设置多个不同难度级别的挑战性任务,并自动评测,节省教师工作量的同时,让学生获得数字系统开发的成就感。

|-基本能力训练/

| |--VerilogHDL语言/

| | |--基本练习/

| | | |--单个wire

| | | |--四位wire

| | | |--反相器

| | | |--与门

| | | |--或非门

| | | |--异或门

| | | |--wire的声明

| | |--向量练习/

| | | |--向量基础

| | |--模块练习:层次/

| | | |--位置连接端口

| | | |--名字连接端口

| | | |--多个模块

| | | |--加法减法器

| | |--过程练习/

| | | |--always块(组合逻辑)

| | | |--always块(时序逻辑)

| | | |--if 语句

| | | |--case语句

| | | |--避免锁存器产生

| | |--Verilog其它特征/

| | | |--三目运算符

| | | |--减操作符

| |--电路/

| | |--组合逻辑/

| | | |--基本门电路

| | | |--多路选择器

| | | |--运算电路

| | | |--由卡诺图到电路

| | |--时序逻辑/

| | | |--锁存器和D触发器

| | | |--计数器

| | | |--移位寄存器

| | | |--更多电路

| | | |--有限状态机

| | |--更复杂电路/

| | | |--1000位进1计数器

| | | |--有限状态机:带使能的移位寄存器

| |--验证:读懂仿真/

| | |--找到代码中的bug/

| | | |--多路选择器

| | | |--与非电路

| | | |--加减法电路

| | | |--case语句电路

| | |--从仿真波形建立电路/

| | | |--组合逻辑电路/

| | | |--时序逻辑电路/

| |--验证:写teatbench/

| | |--周期性时钟产生电路

| | |--与门测试电路

|

|-数字逻辑实验/

| |--组合逻辑设计/

| | |--四位乘法器

| | |--八位乘法器

| | |--四位除法器

| | |--八位乘法器

| | |--八位逐位进位加法器

| | |--八位超前进位加法器

| | |--八位选择进位加法器

| |--时序逻辑设计/

| | |--完成在七段数码管上滚动显示学号

| | |--按键输入学号,并循环显示

| | |--SRAM芯片数据存取

| |--状态机练习/

| | |--验证1101序列(Mealy型)

| | |--验证1101序列(Moore型)

| | |--验证1000序列

| | |--电梯控制器

| |--复杂数字系统设计/

| | |--简单处理器的ASM设计

| | |--流水线乘法器设计

|

|-计算机组成原理实验/

| |--取指模块设计

| |--寄存器堆设计

| |--存储单元设计

| |--算术逻辑单元设计

| |--控制器设计

| |--完整CPU设计